# 正基科技股份有限公司

# AP12611\_M2 Evaluation Board User Manual

#### Address:

6F., No. 23, Huanke 1st Rd., Zhubei City, Hsinchu County 302047, Taiwan

Website: http://www.ampak.com.tw/

## Revision

| Revision | Date       | Description      | Revised By |

|----------|------------|------------------|------------|

| 0.1      | 2024/09/27 | Initial released | Gary       |

|          |            |                  |            |

|          |            |                  |            |

|          |            |                  |            |

|          |            |                  |            |

|          |            |                  |            |

|          |            |                  |            |

## Contents

| Re | vision |                                  | 1 |

|----|--------|----------------------------------|---|

| 1. | EVB    | Introduction                     | 2 |

|    |        | Function Verification Step       |   |

|    |        | WiFi SDIO                        |   |

|    |        | SDIO Hardware Setup              |   |

|    | 2.3    | WiFi Software Setup              | Ę |

| 3. |        | tooth Function Verification Step |   |

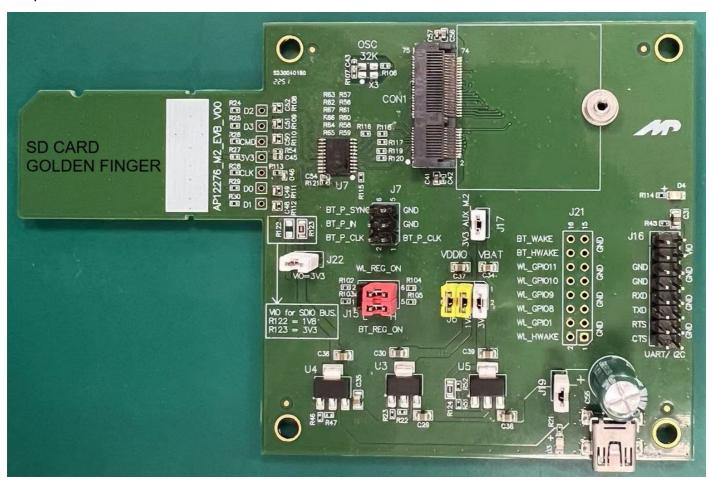

AP12611\_M2 Evaluation board (EVB) likes as figure1. That is designed for IEEE802.11 a/b/g/n/ac/ax WLAN with integrated Bluetooth application. It is subject to provide a convenient environment for customer's verification on WiFi or Bluetooth function. There are many controller pins and reserved GPIO on Evaluation board which describes as below.

Figure 1. Top view of AP12611\_M2 EVB

#### Interface highlights:

- 1. CON1: AP12611 M2 SIP module.

- 2. J16: UART interface connects with UART transport board for BT measuring

- 3. J15: Enable(H) or disable(L) Bluetooth, WiFi function

- 4. J6: VBAT / WL\_VIO / BT\_VIO for main system I/O power path.

- 5. J20: 5V DC mini USB input connector.

- 6. J8: Standard SDIO interfaces for Wi-Fi performance measured.

- 7. J21: WL HOST WAKE/BT HOST WAKE/BT DEV WAKE/WL GPIOs.

- 8. J7: BT PCM interface.

- 9. J17: CON1 3.3V Power

AMPAK Technology Inc.

## 2. WiFi Function Verification Step

#### 2.1 WiFi SDIO

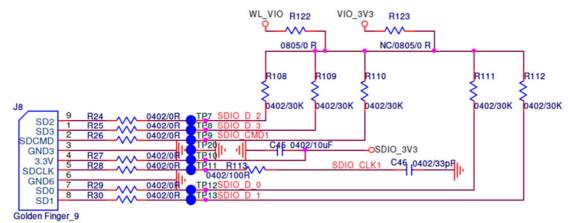

Using external pull up resistors depends on the SDIO supply voltage. The resistance range is 30  $K\Omega$ ~40  $K\Omega$  on the four data lines and the CMD line as the following circuitry.

|                | R122 | R123 | R108 | R109 | R110 | R111 | R112 | C46  |

|----------------|------|------|------|------|------|------|------|------|

| VIO=3.3V for   |      |      |      |      |      |      |      |      |

| Host           | N/A  | 0R   | 200R | 200R | 1KR  | 200R | 200R | 33pF |

| (SDIO_2.0)     |      |      |      |      |      |      |      |      |

| VIO=1.8V       |      |      |      |      |      |      |      |      |

| For Host       | 0R   | N/A  | 30KR | 30KR | 30KR | 30KR | 30KR | N/A  |

| (SDIO_2.0/3.0) |      |      |      |      |      |      |      |      |

Figure 2. WiFi verification connection interface to Host SDIO as using SDIO2.0

Figure 3. EVB interface to HOST SDIO 2.0.

Figure 4. EVB interface to HOST SDIO 3.0.

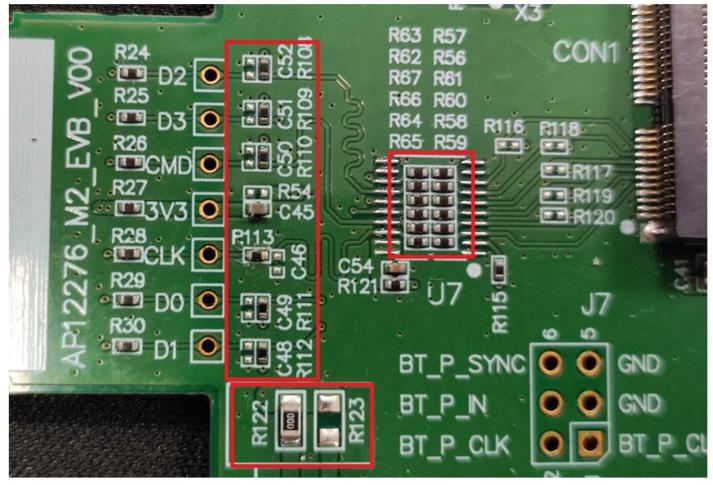

- ♦ SDIO 2.0 Hardware Setup:

- ♦ Pull up voltage should be 3.3V, so make sure R123 is existed.

- ♦ U7 placed, R56/ R57/ R58/ R59/ R60/ R61/ R62/ R63/ R64/ R65/ R66/ R67 NOP.

- ♦ SDIO 3.0 Hardware Setup:

- ♦ Pull up voltage should be 1.8V, so make sure R122 is existed.

- ♦ R56/ R57/ R58/ R59/ R60/ R61/ R62/ R63/ R64/ R65/ R66/ R67 placed, U7 NOP.

#### 2.2 SDIO Hardware Setup

- Refer to Figure 2 SDIO pin definition connects the J8 interface of AP12611\_M2 evaluation board to Host SDIO control interface.

- ❖ Using pull high resistors (R108, R109, R110, R111, R112) that resistance is 30Kohm for 1.8V or 3.3V VDDIO pull up voltage. (Pull high resistors are un-necessary if at verification phase.)

- ❖ Connects an external antenna at SMA connector on the evaluation board.

- ❖ Note to the VDDIO voltage level should be the same with GPIO voltage level of Host CPU.

### 2.3 WiFi Software Setup

Please follow up software guideline of Ampak official released.

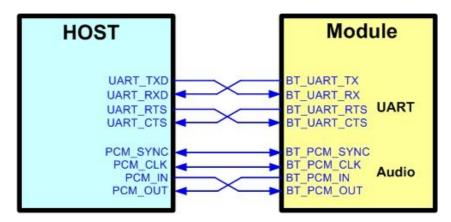

## 3. Bluetooth Function Verification Step

Figure 5. Bluetooth verification connection interface to Host UART

#### Hardware Setup:

- ❖ Refer to Figure 5 UART pin definition connects the J16 interface of AP12611 evaluation board to Host UART control interface.

- Connects an external antenna at SMA connector on the evaluation board.

- Note to the VDDIO voltage level should be the same as GPIO voltage level of Host CPU.

#### WiFi and Bluetooth software setup:

Please follow up software guideline of Ampak official released.